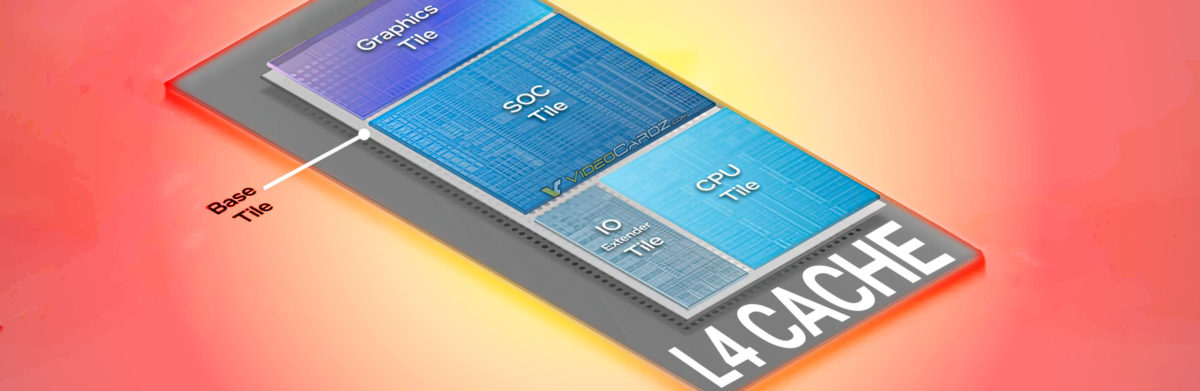

Ya sabíamos por un informe reciente que «Meteor Lake» introduce una caché L4, y ahora nos enteramos de que su nombre en clave es «Adamantine» y cumple funciones similares a las de un intercalador pasivo. La próxima microarquitectura «Meteor Lake» de Intel impulsará el primer procesador desagregado de la compañía para el segmento cliente.

Un procesador desagregado es diferente de un MCM (como «Clarkdale»), ya que los componentes más finos que conforman el procesador, que de otro modo no podrían existir en sus propios paquetes sin una latencia extrema, se hacen compartir un único paquete a través de una interconexión de alta velocidad. Esta desagregación obedece a razones puramente económicas, de modo que la empresa no necesita utilizar el nodo de fundición más reciente (y caro) para todo el procesador, sino que lo raciona a los componentes específicos que más se benefician de ello. A diferencia de los procesadores cliente de AMD, que disgregan los núcleos de la CPU y el resto de E/S del procesador en dos tipos de chipslets, en Intel «Meteor Lake» no sólo se disgregarán los núcleos de la CPU (compute tile), sino también la iGPU en su propio tile, además de la E/S de la plataforma en tiles separados todavía.

Hasta ahora, se creía que la innovación de empaquetado Foveros de Intel, que elimina la necesidad de un costoso intercalador de silicio, facilitaría las comunicaciones entre los distintos mosaicos, pero ahora nos enteramos de que el procesador contará de hecho con una memoria caché L4 que proporciona capacidades de intercalación pasiva. Por sí mismo, un intercalador de silicio no tiene lógica. Su única función es servir de base para que las distintas placas lógicas y de memoria se asienten encima, de modo que podría proporcionar un cableado microscópico de alta densidad entre ellas, que de otro modo no sería posible a través del sustrato de fibra de vidrio del encapsulado. Una caché L4 es otra cosa, y «Meteor Lake» presenta una caché L4 que actúa como baldosa base y como intercalador pasivo (un término erróneo si se entiende cómo funciona). Esta baldosa ha recibido el nombre en clave de «Adamantine».

«Adamantine» es un azulejo base con una memoria caché de nivel 4 (L4). Se desconoce el soporte físico (si se trata de una SRAM cara o de una eDRAM), y el tamaño variaría entre las distintas variantes de «Meteor Lake», pero lo que hace esencialmente es interconectar las distintas losetas a través de la memoria caché. Mientras que un intercalador «activo» es una pieza muda de silicio con cableado de alta densidad, como hemos explicado antes, un intercalador «pasivo» es una memoria con conexiones a las distintas fichas.

Para que una ficha se comunique con otra, los datos con las etiquetas adecuadas se retiran a esta caché L4, que luego es recogida por su ficha destinataria. En esencia, se trata del mismo modo en que funcionan las cachés L3 compartidas de los procesadores Intel, que es como se comunican entre sí los núcleos de la CPU, la iGPU y los componentes uncore. Si ampliamos este concepto a un nivel de procesador desagregado, entenderemos cómo funciona la caché L4. Los tiles individuales tienen sus propias «cachés de último nivel» (LLC) a nivel local. El Compute Tile, por ejemplo, tiene una caché L3 compartida entre los clusters P-cores y E-core. Esta es la caché L3 que se expone al sistema operativo.

Para que quede claro, «Meteor Lake» sigue teniendo conexiones de datos directas entre las distintas placas, pero estas conexiones no siguen una topología radial (en la que cada placa está conectada directamente a todas las demás). Sólo el módulo SoC parece tener conexiones de matriz a matriz con el módulo de cálculo (núcleos de CPU), el módulo de gráficos (iGPU), el módulo de E/S y el PMC. En los casos en los que, por ejemplo, el módulo de cálculo quiera comunicarse con el módulo de gráficos, la caché L4 servirá como ruta de latencia más baja que a través del módulo SoC.

El tamaño de la caché L4 no se conoce realmente, pero si se basa en un medio físico más lento que la SRAM que compone la caché L3 de la Compute Tile, es lógico pensar que su tamaño será considerablemente mayor. Según «Moore’s Law is Dead», se están probando tamaños de caché L4 del orden de 128 MB a 512 MB, aunque podrían llegar incluso a gigabytes, señala el canal tecnológico.