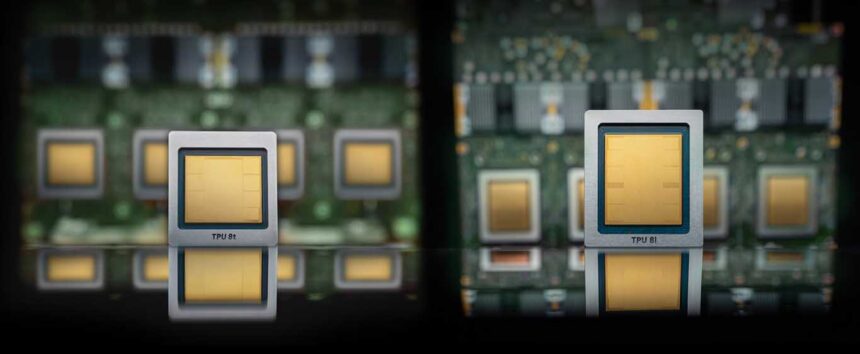

En Google Cloud Next, presentamos la octava generación de la Unidad de Procesador Tensor (TPU) personalizada de Google, que llegará próximamente con dos arquitecturas distintas y diseñadas específicamente para entrenamiento e inferencia: TPU 8t y TPU 8i. Estos dos chips están diseñados para alimentar nuestros superordenadores personalizados, para impulsar desde el entrenamiento de modelos de vanguardia y el desarrollo de agentes hasta enormes cargas de inferencia. Los TPUs llevan años impulsando modelos base líderes, incluido Gemini. Estos TPUs de octava generación juntos ofrecerán escala, eficiencia y capacidades a través de cargas de entrenamiento, servicio y agentes.

En esta era de agentes de IA, los modelos deben razonar ante los problemas, ejecutar flujos de trabajo en varios pasos y aprender de sus propias acciones en bucles continuos. Esto plantea un nuevo conjunto de demandas para la infraestructura, y los TPU 8t y TPU 8i fueron diseñados en colaboración con Google DeepMind para asumir las cargas de trabajo de IA más exigentes y adaptarse a las arquitecturas de modelos en evolución a gran escala.

Las TPUs establecen el estándar para varios componentes de supercomputación de ML, incluyendo números personalizados, refrigeración líquida, interconexiones personalizadas y más, y nuestras TPUs de octava generación son la culminación de más de una década de desarrollo. La clave detrás del diseño original de la TPU sigue vigente hoy en día: al personalizar y co-diseñar silicio con hardware, redes y software, incluyendo la arquitectura del modelo y los requisitos de la aplicación, podemos ofrecer una eficiencia energética y un rendimiento absoluto mucho mayores.

Estamos encantados de ver cómo una década de innovación se traduce en avances reales. Hoy en día, organizaciones pioneras como Citadel Securities están empujando los límites de lo posible, eligiendo TPUs para impulsar sus cargas de trabajo de IA de vanguardia:

Hemos podido ejecutar nuestras cargas de trabajo más exigentes de dos a cuatro veces más rápido y a un coste un 30% menor gracias a las TPUs Ironwood de 7ª generación de Google Cloud. Nuestro equipo está entusiasmado por aprovechar el Hiperordenador de IA de Google Cloud con las arquitecturas TPU 8t y TPU 8i de próxima generación para transformar aún más nuestra economía de formación y ampliar los límites de la escalabilidad. Josh Woods, CTO, Citadel Securities

Dos fichas para cumplir el momento

Los ciclos de desarrollo de hardware son mucho más largos que los del software. Con cada generación de TPUs, debemos considerar qué tecnologías y demandas existirán cuando lleguen al mercado. Hace varios años, anticipábamos un aumento en la demanda de inferencia por parte de los clientes a medida que se despliegan modelos de IA vanguardistas en producción y a gran escala. Y con el auge de los agentes de IA, determinamos que la comunidad se beneficiaría de chips especializados individualmente para las necesidades de entrenamiento y servicio.

TPU 8t destaca en cargas de entrenamiento masivas e intensivas en computación, diseñadas con mayor rendimiento de cómputo y mayor ancho de banda de escalabilidad. TPU 8i está diseñado con más ancho de banda de memoria para atender las cargas de inferencia más sensibles a la latencia, lo cual es fundamental porque las interacciones entre agentes a gran escala amplifican incluso pequeñas ineficiencias.

Es importante destacar que ambos chips pueden ejecutar diversas cargas de trabajo, pero la especialización desbloquea eficiencias y ganancias significativas.

TPU 8t: La potencia del entrenamiento

TPU 8t está diseñado para reducir el ciclo de desarrollo del modelo frontera de meses a semanas. Equilibrando el mayor rendimiento de computación posible, memoria compartida y ancho de banda entre chips con la mejor eficiencia energética y tiempo de cómputo productivo, hemos creado un sistema que ofrece casi 3 veces el rendimiento de cómputo por pod respecto a la generación anterior, permitiendo una innovación más rápida para asegurar que nuestros clientes sigan marcando el ritmo de la industria.

- Escala masiva: Un único superpod TPU 8t ahora escala a 9.600 chips y dos petabytes de memoria compartida de alto ancho de banda, con el doble del ancho de banda entre chips de la generación anterior. Esta arquitectura ofrece 121 ExaFlops de computación y permite que los modelos más complejos aprovechen un único y enorme conjunto de memoria.

- Máxima utilización: Al integrar también un acceso de almacenamiento 10 veces más rápido, combinado con TPUDirect para extraer datos directamente al TPU, TPU 8t ayuda a garantizar la máxima utilización del sistema de extremo a extremo.

- Escalado casi lineal: Nuestra nueva red Virgo, combinada con JAX y nuestro software Pathways, significa que TPU 8t puede ofrecer escalabilidad casi lineal para hasta un millón de chips en un solo clúster lógico.

Además del rendimiento bruto, TPU 8t está diseñado para alcanzar más del 97% de «goodput» —una medida de tiempo de cómputo útil y productivo— mediante un conjunto completo de capacidades de Fiabilidad, Disponibilidad y Servicio (RAS). Estas incluyen telemetría en tiempo real a través de decenas de miles de chips, detección y redirección automática alrededor de enlaces ICI defectuosos sin interrumpir un trabajo, y Conmutación de Circuitos Ópticos (OCS) que reconfigura el hardware alrededor de fallos sin intervención humana.

Cada fallo de hardware, parón de red o reinicio de puntos de control es el tiempo que el clúster no está entrenando, y a escala de entrenamiento de frontera, cada punto porcentual puede traducirse en días de entrenamiento activo.

En la era agente, los usuarios esperan poder hacer preguntas, delegar tareas y obtener resultados. TPU 8i está diseñado para manejar el trabajo intrincado, colaborativo e iterativo de muchos agentes especializados, que a menudo «se agrupan» en flujos complejos para ofrecer soluciones e ideas para las tareas más desafiantes. Rediseñamos la pila para eliminar el efecto de «sala de espera» mediante cuatro innovaciones clave:

- Romper el «muro de memoria»: Para evitar que los procesadores permanezcan inactivos, el TPU 8i combina 288 GB de memoria de alto ancho de banda con 384 MB de SRAM en el chip—3 veces más que la generación anterior—manteniendo el conjunto de trabajo activo del modelo completamente integrado.

- Eficiencia impulsada por Axion: Duplicamos el número de hosts físicos de CPU por servidor, pasando a nuestras CPUs personalizadas basadas en Axion Arm. Al usar una arquitectura de memoria no uniforme (NUMA) para aislamiento, hemos optimizado todo el sistema para un rendimiento superior.

- Escalado de modelos MoE: Para modelos modernos de Mezcla de Expertos (MoE), duplicamos el ancho de banda de Interconexión (ICI) a 19,2 Tb/s. Nuestra nueva arquitectura Boardfly reduce el diámetro máximo de la red en más de un 50%, asegurando que el sistema funcione como una unidad cohesiva y de baja latencia.

- Eliminar el lag: Nuestro nuevo Collective Acceleration Engine (CAE) integrado en chip descarga las operaciones globales, reduciendo la latencia en chip hasta 5 veces y minimizando el lag.

Estas innovaciones ofrecen un 80% mejor en cuanto a un rendimiento por dólar en comparación con la generación anterior, permitiendo a las empresas atender casi el doble de volumen de clientes al mismo coste.

Co-diseñado para Géminis, abierto a todos

Este TPU de octava generación es también la última expresión de nuestra filosofía de co-diseño, donde cada especificación está diseñada para resolver los mayores obstáculos de la IA.

- La topología Boardfly fue diseñada específicamente para las demandas de comunicación de los modelos de razonamiento más capaces de la actualidad.

- La capacidad de SRAM en TPU 8i se ajustó a la huella de caché KV de los modelos de razonamiento a escala de producción.

- Los objetivos de ancho de banda del tejido de Virgo Network se derivaron de los requisitos de paralelismo del entrenamiento de un billón de parámetros.

Y por primera vez, ambos chips funcionan en el propio host de CPU basado en Axion Arm de Google, lo que nos permite optimizar todo el sistema, no solo el chip, en rendimiento y eficiencia.

Ambas plataformas soportan JAX nativo, MaxText, PyTorch, SGLang y vLLM —los frameworks que ya usan los desarrolladores— y ofrecen acceso bare metal, ofreciendo a los clientes acceso directo al hardware sin la sobrecarga de la virtualización. Contribuciones de código abierto, incluyendo MaxText referencian implementaciones y Tunix para aprendizaje por refuerzo, son caminos llave en mano entre el despliegue de capacidades y producción.

Diseñando para la eficiencia energética a gran escala

En los centros de datos actuales, la energía, no solo el suministro de chips, es una limitación vinculante. Para solucionar esto, hemos optimizado la eficiencia en toda la pila, con una gestión integrada de energía que ajusta dinámicamente el consumo en función de la demanda en tiempo real. TPU 8t y TPU 8i ofrecen hasta el doble de rendimiento por vatio respecto a la generación anterior, Ironwood.

Pero la eficiencia en Google no es solo una métrica a nivel de chip; también es un compromiso a nivel de sistema que va desde el silicio hasta el centro de datos. Por ejemplo, integramos conectividad de red con computación en el mismo chip, reduciendo significativamente los costes energéticos de mover datos a través del TPU pod. Incluso nuestros centros de datos están co-diseñados con nuestros TPUs. Innovamos tanto en hardware como en software para permitir que nuestros centros de datos entregaran seis veces más potencia de cálculo por unidad de electricidad que hace solo cinco años.

TPU 8t y TPU 8i continúan en esa trayectoria. Ambos están respaldados por nuestra tecnología de refrigeración líquida de cuarta generación que mantiene densidades de rendimiento que la refrigeración por aire no puede. Al poseer toda la pila, desde el host Axion hasta el acelerador, podemos optimizar la eficiencia energética a nivel de sistema de formas que simplemente no se pueden lograr cuando el host y el chip están diseñados de forma independiente.

Infraestructura para la era agente

Cada gran transición informática ha requerido avances en infraestructura, y la era agente no es diferente. La infraestructura debe evolucionar para satisfacer las demandas de agentes autónomos que operan en bucles continuos de razonamiento, planificación, ejecución y aprendizaje.

TPU 8t y TPU 8i son nuestra respuesta a este desafío: dos arquitecturas especializadas diseñadas para redefinir lo posible en IA, desde construir los modelos de IA más capaces, hasta enjambres de agentes perfectamente orquestados, pasando por gestionar las tareas de razonamiento más complejas. Ambos chips estarán disponibles de forma general a finales de este año y podrán usarse como parte del AI Hypercomputer de Google, que reúne hardware diseñado específicamente (computación, almacenamiento, redes), software abierto (frameworks, motores de inferencia) y consumo flexible (orquestación, gestión de clústeres y modelos de entrega) en una pila unificada.

La computación agente redefinirá lo que es posible. Estamos encantados de anunciar la última encarnación de nuestra incansable innovación para impulsar esta transformación, TPU 8i y 8t. Los clientes interesados pueden solicitar más información.